Myricom DBL

Enable Advanced Financial Trading Capabilities

Accelerate Your Trading Application

With Extreme Low-Latency and Advanced Functions

The Myricom DBL® technology powers the ARC Series of network adapters, driving down system-level Tick-To-Trade latency, enabling advanced financial trading capabilities and MiFID II reporting regulations. It is a tightly-integrated combination of FPGA firmware and software libraries.

Deployment Options

The Myricom DBL software is deployable on the Myricom ARC Series D-Class and E-Class SmartNICs. These 10GbE network adapters provide the low latency and high bandwidth demanded to for high-frequency trading applications.

System-level Tick-To-Trade latency

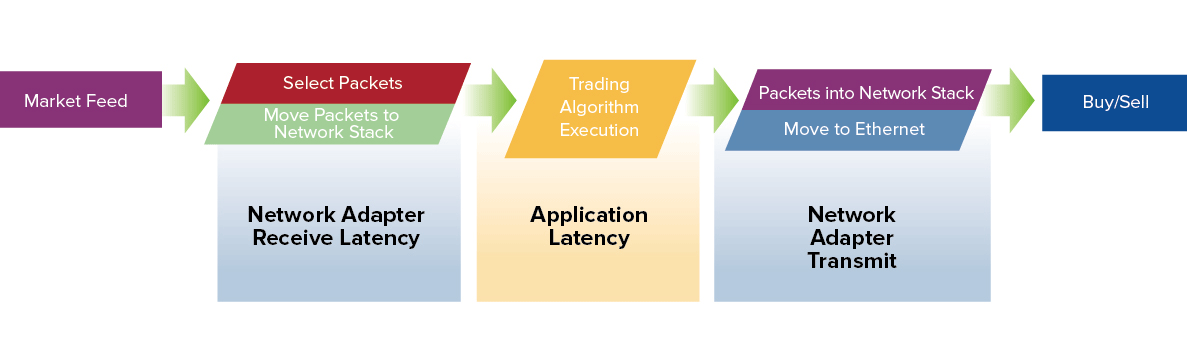

To win against your competition, and make money, you need to squeeze down the time between receiving a market tick favorable to your algorithm and sending out the TRADE order. DBL® drives down Tick-To-Trade latency at multiple points in the trading process, allowing your application to avoid slippage and deliver higher fill rates.

Optimize the way you receive market data

First, DBL minimizes Receive Latency by exploiting the parallel processing capabilities of powerful FPGAs to direct subsets of a multi-cast market feed to specified CPU cores, totally bypassing the OS kernel.

At initialization, your application uses our DBL software library for a quick and easy set-up of the selectors, targeting data from a specific address and port to an assigned ring.

Every packet does not need to move into the user space data rings, just the packets your application uses.

Accelerate your application layer

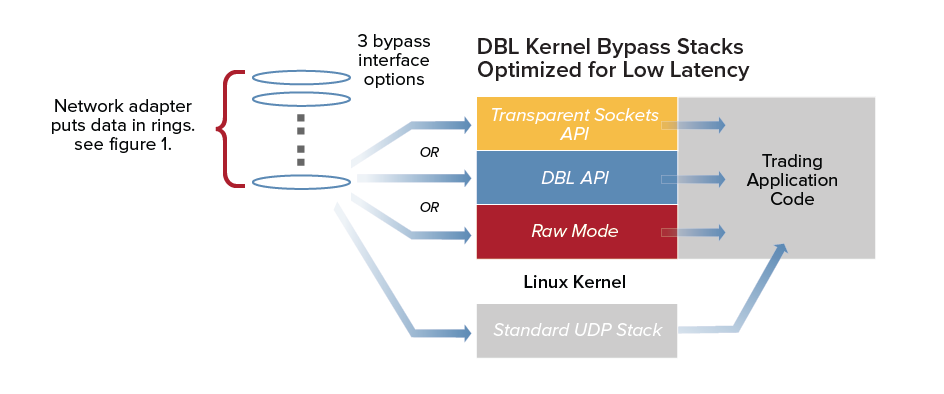

DBL software accelerates trading algorithms with Kernel Bypass Stacks, which move UDP packets directly into user space. Doing that eliminates the cost of CPU context switches and also enables deployment of special-purpose network stacks in user space, which are faster than the general purpose stacks inside the kernel. The DBL has 3 interface options for these faster network stacks:

- Transparent Sockets accelerate stack performance without code changes. Standard socket calls access the low latency DBL stack without recompiling.

- The DBL API accesses a set of Myricom-optimized sockets. It requires a software recompile, with renamed socket calls, but delivers even lower latency.

- Raw Mode allows customers to implement their own custom stacks, using either raw sockets or a proprietary API.

System-level Tick-To-Trade latency

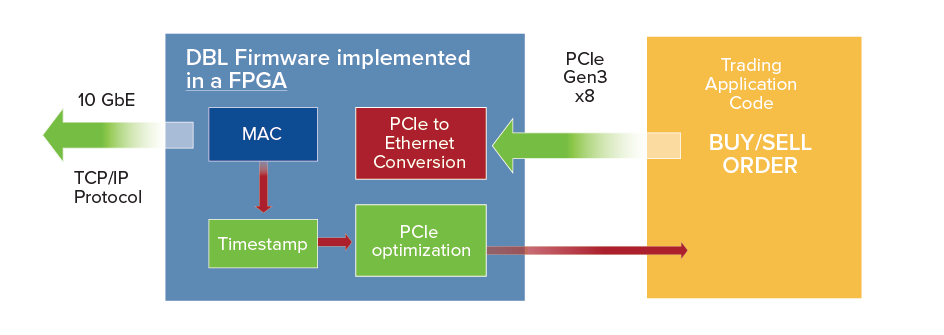

DBL software accelerates outbound order processing by pre-populating the TCP/IP stack in user space, then filling in just the variable information from the application before sending the BUY/SEL order packet to the adapter. This Send Latency is further minimized with extremely efficient PCIe to Ethernet conversion firmware. Each new generation of FPGAs represents faster silicon, making the firmware faster and moving Send (and Receive) Latency closer to zero.

Precise Hardware Timestamps Comply

with Looming Regulations

With DBL firmware, Myricom ARC Series network adapters are able to track latency in real-time with less effort and more accuracy than expensive packet capture devices, using precise hardware timestamps on both ingress and egress packets. This unique capability allows your application to calculate latency without needing to tag TCP/IP orders with UDP sequence numbers, for simplified trading performance verification. You can achieve regulatory compliance, including the upcoming MiFID II requirements, by using DBL to create audit trails of trades with both transmit and receive timestamps. An additional timekeeping option is to use ARC Series adapters with Sniffer10G firmware and software in an adjunct system dedicated to recording trade data.

Features:

- 10GbE network adapters lead the industry in system-level Tick-To-Trade Latency

- Tightly integrated FPGA firmware and server software combine to accelerate trading applications

- Precise hardware timestamps on both ingress and egress packets

- Support for Linux and Windows

Specifications

Please see below:

| Specs | Myricom ARC D | Myricom ARC E |

|---|---|---|

| Bus Interface: | PCI Express Gen 3, 8 lanes wide | PCI Express Gen 3, 8 lanes wide |

| Form Factor: | Low-profile PCI Express x8 add-in cards that ship with a standard height faceplate installed; and a low profile faceplate in the box. | Dual port low-profile PCI Express x8 add-in cards that ship with a standard height faceplate installed; and a low profile faceplate in the box. |

| Electrical Power: | 24W | 18W – dual port adapter |

| Cooling Requirements: | It is recommended that adapters be installed into servers that provide some air flow over the PCIe slots. Use in an office or computer room environment. | It is recommended that adapters be installed into servers that provide some air flow over the PCIe slots. Use in an office or computer room environment. |

| Cooling Options: | Active Cooling | Active cooling |

| Operating Temperature: | 0-55 deg C (100 LFM min) | 0-55 deg C (100 LFM min) |

| Storage Temperature: | -40 to 70 deg C | -40 to 70 deg C |

| Storage Humidity: | 5% to 90% non-condensing | 5% to 90% non-condensing |

| Processor: | FPGA | FPGA |

| Hardware Acceleration: | N/A | N/A |

| Memory: | No user programmable memory. | No user programmable memory. |

| Network Connectivity: | 2×10 Gb Ethernet, SFP+ | 2×10 Gb Ethernet, SFP+ |

| Software Support: | Software available for Linux (CentOS, RHEL and Ubuntu) and Windows. Supports libpcap (Linux) and winpcap (Windows) libraries. Software provides support for RSS (receive side scaling), port merging of ethernet packets, pcap replay | Software available for Linux (CentOS, RHEL and Ubuntu) and Windows. Supports libpcap (Linux) and winpcap (Windows) libraries. Software provides support for RSS (receive side scaling), port merging of ethernet packets, pcap replay |

| SW Version supported: | DBL V5.0.7 | DBL V5.0.7; No ethernet driver |

| Security: | N/A | N/A |

| Timestamp: | +/-100 ns accuracy | +/-100 ns accuracy |

| Throughput: | 2x10Gb/s | 2x10Gb/s |

Order Details

Please see below:

| Model Number | Product Description |

|---|---|

| 10G-PCIE3-8D-2S+DBL | Dual Port, 10 Gb/sec PCIe Gen3 x8 NIC with 2 SFP+ adapters and DBL Software. |

| 10G-PCIE3-8E-2S+DBL | Dual SFP+ board using K35 FPGA with DBL license. Full height bracket pre-installed. |

| 10G-PCIE3-8EL-2S+DBL | Dual SFP+ board using K35 FPGA with DBL license. Low profile bracket pre-installed. |

OEM

| Model Number | Product Description |

|---|---|

| 10G-PCIE3-8EL-2S+DBL | Dual SFP+ board using K35 FPGA with DBL License. Low profile bracket pre-installed. |

| SPT-10G-PCIE3-8EL-2S+DBL | Annual support for Dual SFP+ board using K35 FPGA with DBL license. Includes software updates and email support. |

| OEM Datasheet | See OEM product datasheet. |

Warranty and Support

One year for hardware defects and 90 days for software defects. 90 days of “getting started” telephone and email support, as well as any software upgrades shipped within that window. Refer to the support datasheet for options extending the 90-day window.

Downloads

Visit our Download Center for the latest software, as well as other resources such as user guides and FAQ documents.

Resources and Related Content

Resources

News

ARIA Cybersecurity Solutions, a leading provider of cybersecurity solutions, recognizes Information Systems for Trading (IST) as a premier reseller in the Jordan and Iraqi…

ARIA Cybersecurity Solutions has joined Rockwell Automation’s PartnerNetwork™ as a Technology Partner. Through PartnerNetworkTM, customers can quickly locate complementary products that best solve application…

ARIA Cybersecurity Solutions, a CSPi business (NASDAQ: CSPi), has announced that its breakthrough solution for protecting Operational Technology (OT) environments, AZT PROTECT™, has won…

Blog

Events

Drive trading capabilities with heightened efficiency.